Analog to Digital Converters, ADC, provide digital representations of analog voltages/power for digital signal processing and control circuitry.

As sampling rates increase, problems of temperature drift, noise, aperture uncertainty and many more factors are exacerbated. Around 1978 a very bright Engineering Technician ( Bob ), conceived a design using flash ADCs and Digital to Analog Converters, DAC, comparators and summing circuits, to sample analog signals. This evolved into the early Delta Sigma ADC. It was a lot different from today's versions.

For each ADC bit, we can derive 3 dB better resolution in the analysis of the actual sampled voltage. Conventional ADC designs required doubling most of the circuitry for each extra bit of dynamic range. Currently ADCs can sample at over 5 Giga Samples/Second. I propose an enhanced modified Delta Sigma ADC that dramatically increases the dynamic range of very high speed ADCs without the penalty of an enormous array of comparators and Resistor ladder circuits which generate a lot of electrical noise and HEAT.

An adjunct ADC will be slower with many more bits of resolution. This provides dynamically derived "Temporary Reference Standard" voltage representations. We use this very high dynamic range ADC output to feed a DAC to provide the standard voltage against which we compare the differences in new digitized analog voltages. The incoming analog signal is compared with the "Standard" and like the original Delta Sigma approach, provides an error voltage which gets digitized by a very high speed Delta Sigma ADC which continually improves in accuracy, eventually providing over 28 bits of "REASONABLE, GOOD" resolution.

We repeatedly compare the value of this high resolution "Standard", to the output of the first stage of the 5 GS/S Delta Sigma-ADC. We shall find errors. The magnitude and spectral components of these errors will be processed in a Field Programmable Gate Array, FPGA, to derive finer and finer approximations of the System's error factors.

This average compounderror factor allows us to intelligently Dither our computed results without a large excursion in the instantaneous values and steer the system closer to the real values.

Thus, we shall produce a very high speed ADC with over 28 bits of resolution, relatively speaking. This Relative Approximation output will have an effective sampling rate of the 5 Giga Sample/second Sigma Delta ADC core. As faster ADCs are developed this design will accommodate them for continuing improvements without redesign.

We need better dynamic high speed ADC components and sub-systems. Accepting that cannot develop a perfect representation, for now, our best approach is to have a continuously accumulating error correction factor to smoothly adjust the outputs to approach more nearly true representations of the input voltages.

These high Dynamic Range approximations will provide dramatically improved information for seismic analysis, optical processing resolution and sensitivity, Signals Intelligence, RADAR detection, SETI and medical and other fields.

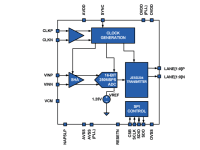

Pictures are of Analog Devices AD7797 ADC and the Intersil 250MSPS 16 Bit ADC.

Thank you, Bob Sommer

Like this entry?

-

About the Entrant

- Name:Robert Sommer

- Type of entry:individual

- Patent status:none