Aircraft/micro-satellites/wearable canteen or backpack computers. All require reduced size & weight, and functional adaptations. The Nano-Frame concept requires the chip industry move forward to the System-On-a-Chip computing slices. This also provides the mechanism and future home for the evolutionary direction we are already heading. Reduced costs, weight, manufacturing efficiency; It all comes together here.

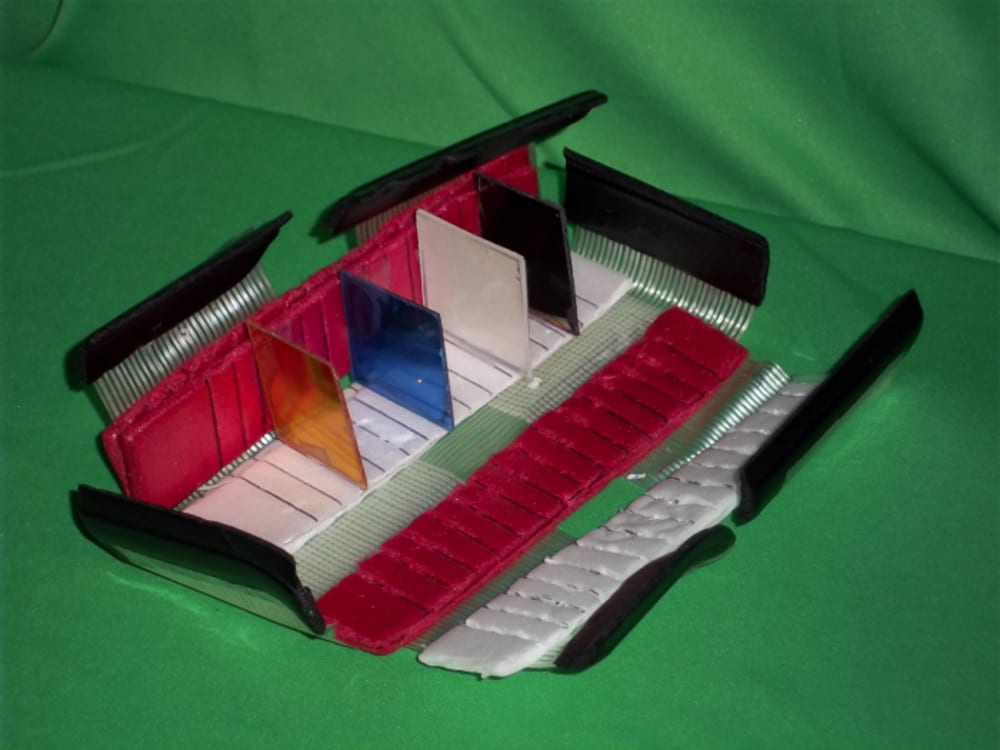

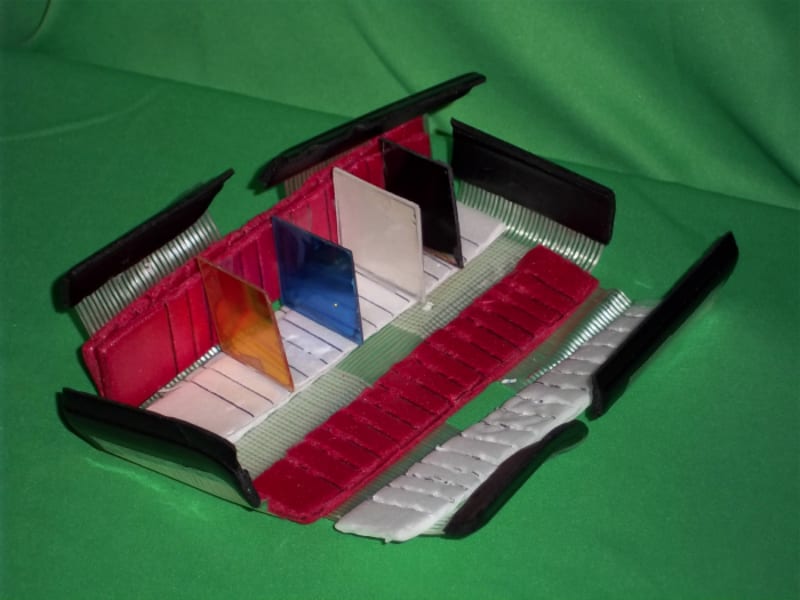

This design comprises SOC functional slices inserted into ceramic rail backplanes. Red for the power bus and white for data communications I/O bus.

This example assumes the black (ops) slice is a software defined radio - intelligence gathering DSP; white a solid state RAM preloaded with OS and mission parameters; blue DSP for k-v-m human interface visualization; and gold the general CPU & controller.

Ceramic rail bus strips have edge connectors, vias, and the longer vertical communication bus lines. This has 15 edge connectors, but if you only need four, space them for cooling. Cooling could be thermo-electric, forced air, or liquid immersion.

Start by pressing the first SOC data slice into a white edge slot, attach an endplate stabilizer (not shown) at the back end and clip it to the white strip. Press in the remaining slices needed. Press this configuration into the red rail. Add additional white & red rails for structural stability and data redundancy. Finally add the other outer stabilizer to the front end. Slide the entire unit into the receiving rails of the container box, rigid dash board, or console. The end stabilizers help contain air flow or coolant flow within, and could be thermal-electric heat exchangers.

Secondly is the dual-frame Nano-Frame configuration. Different SOC slices can handle other tasks, or use similar slices for aerospace & military redundancy. Black connectors with flex circuitry can exchange data between different frames, do redundancy failover /parallelism of like frames, or connect complex configurations to the outside.

Along with future System-On-a-Chip improvements, we also see how minimal communication lines will be needed and standardized by future committees. We have recently seen how multi-wire EIDE disk drive connectors dropped down to just a few lines in SATA drives. Similarly SOC compute slices will require switching to something like SATA, CAT-5 busses, and/or perhaps a TCP-IP variation with each SOC variation having its own MAC subnet address schema for communication to and between slices within the brick. The edge connectors might also have optical grating chirp connectors for the slices inside the brick, along with the typical locator notches.

Possible data slices could be a ring gyro/ GPS/accelerometer guidance controller. SSD memory filled with maps & star charts. Chemistry & chromatographic maps. Entire libraries of formulas segmented by industry and simply call up the mission-defined database needed. Battery & fuel cells. Imagine designing your new SOC slices here. Standardization will be needed in several areas. The examples shown are 1-3/4 x 5 inches and 3 x 5-1/2 inches. Thank you.

Like this entry?

-

About the Entrant

- Name:M. Allen Schultz

- Type of entry:individual

- Patent status:none